# Controlled Growth of Si Nanowires at Low Temperature via the Solid-Liquid-Solid Mechanism

Shiyu Zhang<sup>a</sup>, Weibin Rong<sup>b</sup>, Zhichao Pei, Tao Zou, and Lining Sun

State Key Laboratory of Robotics and Systems Harbin Institute of Technology, Harbin, P. R. China ashi\_yu\_zhang@163.com, brwb@hit.edu.cn

**Keywords:** Si nanowires, low-temperature SLS growth, patterning, mixed catalyst

**Abstract:** This paper provides a novel prospect of low-temperature SLS growth. Large quantities of Si nanowires were manufactured at 600°C under a N2 atmosphere on an N-type Si (100) substrate. Two-dimensional (2D) structures of Si nanowire clusters were gained, by writing the liquid metal ink with especially-designed micropipe pen on the Si wafer, deposited with a gold layer (thickness: ~10 nm). The diameter of the Si nanowire clusters with dot feature and the width of lines can be varied between 500 nm and 50 μm by changing the size of micropipe pen.

#### 1. Introduction

The growth of Si nanowires (Si NWs) are recently researched in Nanofabrication, which has very practical and potential applications in photoluminescence, single-electron devices, photodetectors, nanosensors, and solar cells [1-3]. The general mechanisms of Si NWs growth can be divided into vapor-liquid-solid, vapor-solid-solid, solid-liquid-solid, supercritical fluid-solid-solid and extended vapor-liquid-solid [4-8]. In contrast to the other growth mechanism, solid-liquid-solid (SLS) can directly obtain the silicon source from the Si substrate, making a simple synthetic process and high yield. Yan and Yu first described the synthesis of Si NWs via SLS mechanism. The Si nanowires with diameters ranging from ~10 nm to 50 nm were obtained on silicon (111) substrates deposited a layer of 40 nm Ni at 950°C, Ar (36 sccm) and H<sub>2</sub> (4 sccm) [9-10]. Whereas, the high annealing temperature (1000 °C) has brought great difficulties to the SLS studies of Si NWs during the experiment [11]. The uncontrollability of the formation of Au Island while annealing at high reaction temperature makes it difficult to obtain Si nanowires with diverse controllable patterning. Templates or masks have been used to control the position and size of Si nanowires [12-13], requiring complex processes and high costs.

In this letter, we report a new approach to generate Si nanowires with high density at low temperature (600 °C) by a mixture of gallium-indium (Ga-In) alloys with low eutectic temperature of Ga-In-Si and Au at high Si concentration. By using the mobility of Ga-In, the growth of Si NW clusters of controlled different shapes with point and linear characteristics was achieved by writing liquid metal onto a silicon wafer coated with a layer of ~10 nm gold. The measure of clusters obtained was regulated by different exterior diameters of micropipe pen.

## 2. Materials and Methods

N-type single-crystal Si (100) wafers (thickness:  $500\pm25~\mu m$ ) were used as the substrate (Si source). Following the RCA cleaning steps, the substrate was cleaned in RCA-1 solution (NH4OH (28%):  $H_2O_2$  (30%): DI water 1:1:5 ratio) for 15 min at 70 °C. The oxide layer was removed by HF (6%) for 5 min. RCA-2 (HCL (36%):  $H_2O_2$  (30%): DI water 1:1:5 ratio) was used to remove alkali ions and cations at the final step. Each step of the process was followed by a rinse in deionized water.

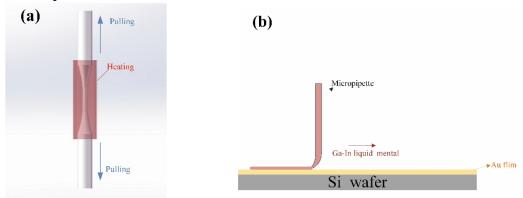

A layer of Au with ~10 nm thickness was deposited on the Si wafers, after RCA cleaning. As shown in Fig. 1(a), the micropipette was produced by micropipette puller from a glass pipe with 1mm outer diameter. By controlling the size and speed of the pulling force, micro nozzles with

different diameters can be obtained, and with the exterior diameter from  $\sim 300$  nm to 50  $\mu$ m were adapted in this experiment.

Figure 1. Schematic diagram of liquid metal direct writing with micropipette pen. (a) manufacturing process for thermal pulling, (b) principle diagram of liquid mental direct writing.

The melting point of Ga-In alloys used in this paper is 16 °C, which maintains good liquidity at room temperature. Fig. 1(b) shows the processing and the principle of this ink direct writing of liquid mental on an Au-coated Si substrate. By using the especially-designed glass microtubules, liquid mental was written on the substrate in different shapes.

The substrate was positioned on a quartz boat in the silica tube heated to 600  $^{\circ}$ C in a  $N_2$  environment (99.99%, 1.5 sccm) for 45 min. To investigate the effect of Ga-In alloys on the SLS growth temperature, samples with only Au were placed inside the silica tube at ~1000  $^{\circ}$ C under  $N_2$  gas flow at 1500 sccm, as a control. Hitachi S-4300 field emission scanning electron microscope (FESEM) was utilized to inspect the surface appearance and microstructures of the growth of Si NWs.

#### 3. Results and discussion

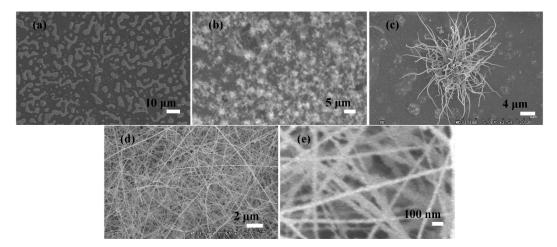

Fig. 2 are the SEM pictures of the Si wafer samples, revealing the impact of Ga-In liquid metal catalyst on the required temperature for Si nanowires growth. Fig. 2(a), (b) are the result of the Si substrates with only a layer of Au as the catalyst at 900 °C and 1000 °C under N<sub>2</sub> flow at 1500 sccm for 45 min, respectively. It can be seen that Si NW nucleation has not yet occurred on the surface with only Au islands in irregular shapes at 900 °C. And the sample at 1000 °C exhibited a mass of Si NWs was synthesized in most areas, which had a flower-like shape in deeper SEM image (FIG. 2 (c)), demonstrating that the annealing temperature of SLS Si NW growth with Au catalyst has to be greater than 1000 °C. In agreement with the conventional SLS Si NW growth with Au catalyst, the diameter of Si NWs is about 300 nm and becomes larger because of the increasing diameter of Au-Si droplets over growth time.

Fig. 2(d), (e) shows that dense silicon nanowires can be obtained at  $600 \,^{\circ}\text{C}$  for 45 min under 1500 sccm  $N_2$  flow, which were both covered with Au and Ga-In alloys. We also observed that the length was much longer which had covered the whole substrate and the diameter (about 50 nm) was much smaller, compared with the Si nanowires on a sample without Ga-In alloys.

We conjecture the above phenomenon that the growth temperature can be reduced from 1000 °C to 600°C with Ga-In alloys is on account of the lower eutectic temperature of Ga-Si and In-Si. Temperature characteristics of Au, Ga and in mental catalysts are listed in Table. 1 by their Alloy Binary Diagram with silicon.

Figure 2. Scanning electron microscopy images of the Au-coated substrates at (a) 900°C and (b) 1000°C. (c) Deeper SEM image of a single cluster from (b), (d) and (e) SEM image of the Si NW growth of sample with Au and Ga-In alloys synthesized at 600°C. The holding time is always 45 min at each growth temperature.

Table.1. Temperature characteristics of Au, Ga and in mental catalysts

| Metal | <b>Eutectic Composition (X, at. %Si)</b> | <b>Melting Point</b> (T <sub>M</sub> , °C) | <b>Eutectic Temperature (T<sub>E</sub>, °C)</b> |

|-------|------------------------------------------|--------------------------------------------|-------------------------------------------------|

| Au    | 18.6                                     | 1064                                       | 363                                             |

| Ga    | 0.0                                      | 30                                         | 29.8                                            |

| In    | 0.004                                    | 157                                        | 156.6                                           |

Adapted from Ref. [14].

Compared with Au which is generally used for various growth of nanowires, Ga and In both have a low  $T_E$  which is very close to their  $T_M$ , but have an especially low composition of silicon in the liquid phase at eutectic point (close to zero). In previous studies, to deal with the low composition problem, plasma-enhanced chemical vapor deposition (PECVD) was used for Si NW growth at a temperature of 500-600 °C for Ga and in, which needs a complicated and high-cost PECVD device [15-16].

In this work, we lowered the Si NW growth temperature successfully by the use of Ga-In with the low eutectic temperature and increased the solubility of Si by the use of Au. Furthermore, each single Si nanowire synthesized with mixed-used catalysts behaved greater in length and diameter than conventional SLS Si NW growth.

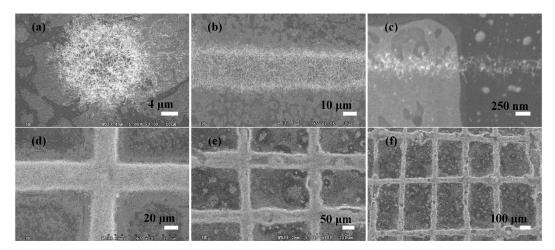

Moreover, another advantage of Ga-In alloys is that they present a liquid phase at room temperature. By utilizing their great mobility, controlled areas of silicon nanowire clusters in different morphologies were fabricated, as shown in Fig. 3. The patterning in point and linear features (shown in Fig. 3(a), (b)) were the simplest Si nanowire cluster structures we can get by the direct writing method above. It is visible that the size of these geometrical features is about 15  $\mu$ m to 50  $\mu$ m. By changing the size of the micropipette, the size of the linear region could be reduced to less than 300 nm (shown in Fig. 3(c)). But because of the high surface tension of liquid metal, the lines of alloys would turn to irregular points. In order to obtain dense and uniform Si nanowires, a micro nozzle with the ~20  $\mu$ m exterior diameter was adapted in this experiment. As shown in Fig.3(d), (e) and (f), the Si NW clusters with a cross and intersecting parallels patterns were fabricated, based on this linear writing of liquid metal. It is believed that this liquid metal direct writing method can be a reliable and flexible method to control the position and size of Si nanowire clusters.

Figure 3. SEM images of Si nanowires with two-dimensional nanostructures. (a) dot-like cluster, (b) and (c) linear cluster, (d) cross cluster of Si NWs, (e) and (f) intersecting parallels cluster.

## 4. Conclusion

A previously unreported SLS growth of Si nanowires at low temperature was achieved in this work. A mixture of Au and gallium-indium alloys catalysts has successfully decreased the annealing temperature of Si nanowire growth (from 1000 °C to 600 °C) via the solid-liquid-solid mechanism. And it was shown that the growth rate increased and the thinner Si NWs were fabricated by additional Ga-In alloys at a lower temperature, consequently.

In addition, various patterns (dots, lines, crosses, and intersecting parallels) of Si nanowire clusters were gained by direct writing of liquid mental with especially-designed micropipe pen. This controllable growth method provides an innovative fabrication of two-dimensional (2D) nanostructures from the bottom up, which is an appealing alternative to conventional top-down processes.

## Acknowledgment

This work was supported by the National Natural Science Foundation of China (grant number 51675141) and the Foundation for Innovative Research Groups of the National Natural Science Foundation of China (grant number 51521003).

#### References

- [1] A. Vena, E. Perret, D. Kaddour, T. Baron, IEEE Trans. Microw. Theory Tech. 64 (2016) 2977-2985.

- [2] M.Y. Shen, B.R. Li, Y.K. Li, Biosens. Bioelectron. 60 (2014) 101-111.

- [3] B. O'Donnell, L. Yu, M. Foldyna, P. R. i Cabarrocas, J. Non-Cryst. Solids 358 (2012) 2299-2302.

- [4] N. Holonyak, C.M. Wolfe, J.S. Moore, Appl. Phys. Lett. 6 (1965) 64-68.

- [5] J.D. Holmes, K.P. Johnston, et al., Science 287 (2000) 1471-1473.

- [6] Y. Li, P. Liang, X. Yang, et al., Mater. Lett. 134 (2014) 5-8.

- [7] T.I. Kamins, R.S. Williams, D.P. Basile, T. Hesjedal, J. Appl. Phys. 89 (2001) 1008-1016.

- [8] H.Y. Tuan, D.C. Lee, T. Hanrath, B. A. Korgel, Nano Lett. 5 (2005) 681-684.

- [9] D.P. Yu, Y.J. Xing, Q.L. Hang, et al., Phys. E 9 (2001) 305-309.

- [10] H.F. Yan, Y.J. Xing, Q.L. Hang, et al., Chem. Phys. Lett. 323 (2000) 224-228.

- [11] J.H. Lee, M.A. Carpenter, R.E. Geer, J. Mater. Res. 26 (2011) 2232-2239.

- [12] A. Soam, N. Arya, A. Singh, R. Dusane, Chem. Phys. Lett. 678 (2017) 46-50.

- [13] T. Shimizu, T. Xie, J. Nishikawa, S. Shingubara, Adv. Mater. 19 (2007) 917-920.

- [14] P. Villars, H. Okamoto, K. Cenzual, Eds., ASM alloy phase diagrams database, (OH): ASM International, Materials Park, USA, 2006. Section editors.

- [15] F. Iacopi, P.M. Vereecken, et al., Nanotechnology 18 (2007) 505307-505307.

- [16] S.J. Rathi, B.N. Jariwala, J.D. Beach, P. Stradins, J. Phys. Chem. C 115 (2011) 3833-3839.